友情提示

本站部分转载文章,皆来自互联网,仅供参考及分享,并不用于任何商业用途;版权归原作者所有,如涉及作品内容、版权和其他问题,请与本网联系,我们将在第一时间删除内容!

联系邮箱:1042463605@qq.com

相关文章

近七日浏览最多

最新文章

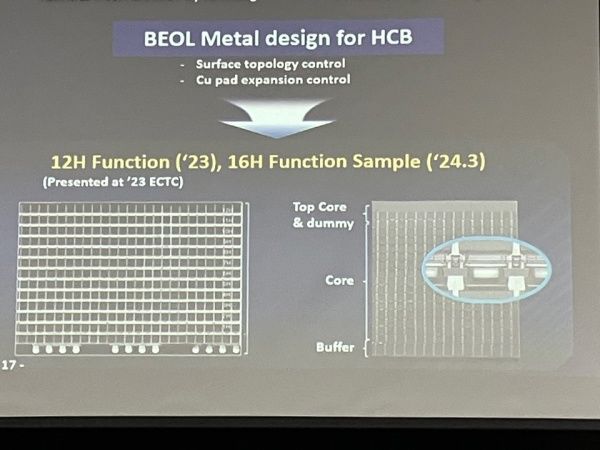

IT之家 4 月 7 日消息,综合韩媒 The Elec 和 ETNews 报道,三星电子先进封装团队高管 Dae Woo Kim 在 2024 年度韩国微电子与封装学会年会上表示近日完成了采用 16 层混合键合 HBM 内存技术验证。

Dae Woo Kim 表示,三星电子成功制造了基于混合键合技术的 16 层堆叠 HBM3 内存,该内存样品工作正常,未来 16 层堆叠混合键合技术将用于 HBM4 内存量产。

相较现有键合工艺,混合键合无需在 DRAM 内存层间添加凸块,而是将上下两层直接铜对铜连接,可显著提高信号传输速率,更适应 AI 计算对高带宽的需求。

混合键合还可降低 DRAM 层间距,进而减少 HMB 模块整体高度,但也面临成熟度不足,应用成本昂贵的问题。

三星电子在 HBM4 内存键合技术方面采用两条腿走路的策略,同步开发混合键合和传统的 TC-NCF 工艺。

结合下方图片和IT之家以往报道,HBM4 的模块高度限制将放宽到 775 微米,有利于继续使用 TC-NCF。

三星正努力降低 TC-NCF 工艺的晶圆间隙,目标在 HBM4 中将这一高度缩减至 7.0 微米以内。

不过 TC-NCF 技术也面临着质疑。Dae Woo Kim 回击称三星电子的方案相较竞争对手 SK 海力士的 MR-RUF 更适合 12 层乃至 16 层的高堆叠模块。

友情提示

本站部分转载文章,皆来自互联网,仅供参考及分享,并不用于任何商业用途;版权归原作者所有,如涉及作品内容、版权和其他问题,请与本网联系,我们将在第一时间删除内容!

联系邮箱:1042463605@qq.com